先进封装技术:在半导体制造中赢得一席之地

时间: 2024-03-28 22:51:34 | 作者: 媒体动态

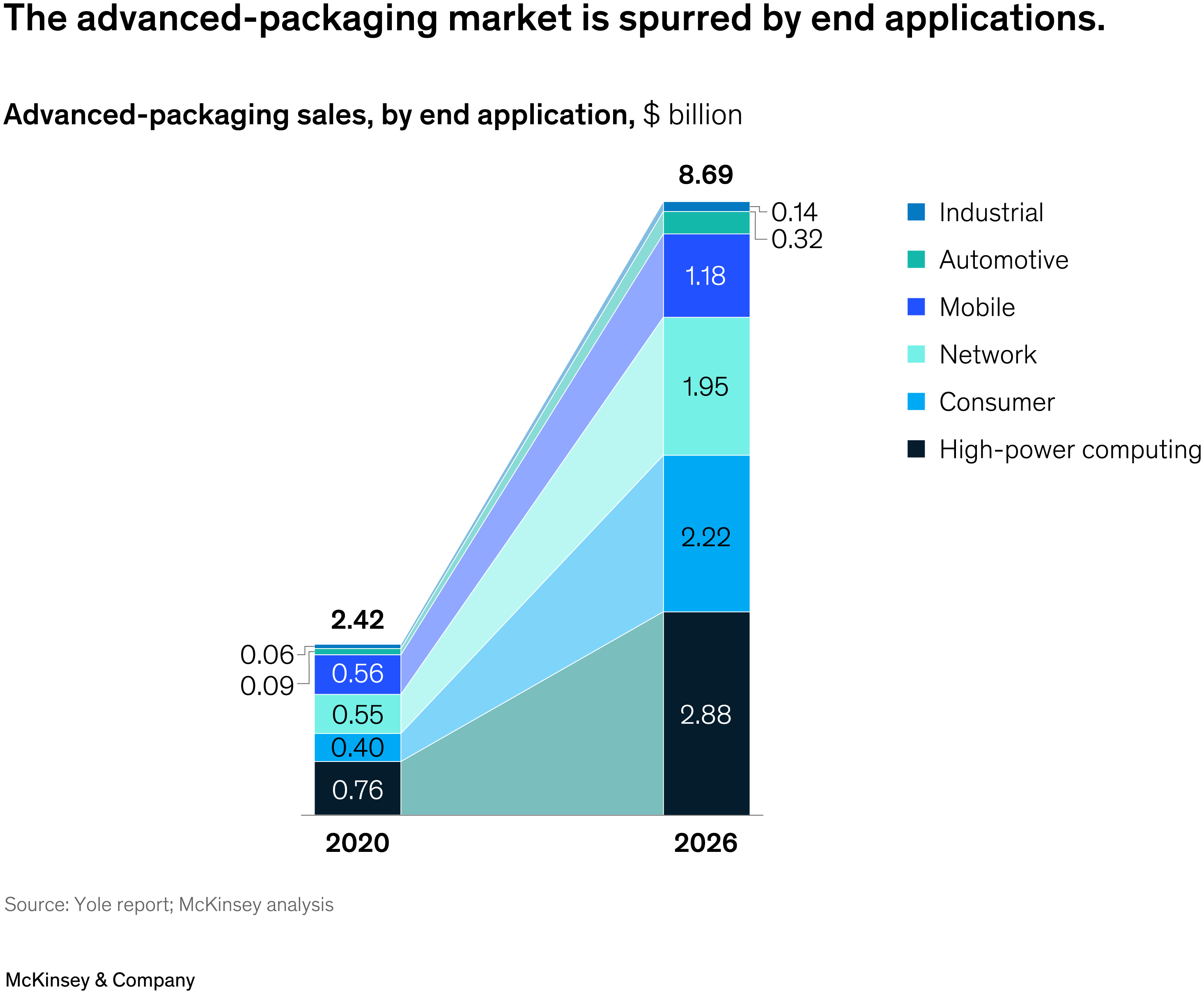

在半导体技术的快速的提升中,摩尔定律一度被视为不可逾越的巅峰,然而随着其优势逐渐达到极限,业界对于芯片性能提升的关注点开始转向后端生产,特别是封装技术的创新。技术,作为半导体技术的下一个突破点,正以其独特的优势引领市场的新一轮增长。

传统上,封装工艺在半导体生产流程中一直被视为后端环节,往往被低估其重要性。原因有两点:首先,使用老一代设备仍旧能封装晶片。其次,封装大多由外包的半导体组装和测试公司(OSAT)完成,这一些企业主要依靠低廉的劳动力成本而非其他差异化竞争。然而,随技术的进步和市场的变化,封装技术不再只是简单的保护芯片免受外界环境侵害的手段,而是成为提升芯片性能、满足新兴应用需求的关键。先进封装技术的出现,正是对这一转变的最好诠释。

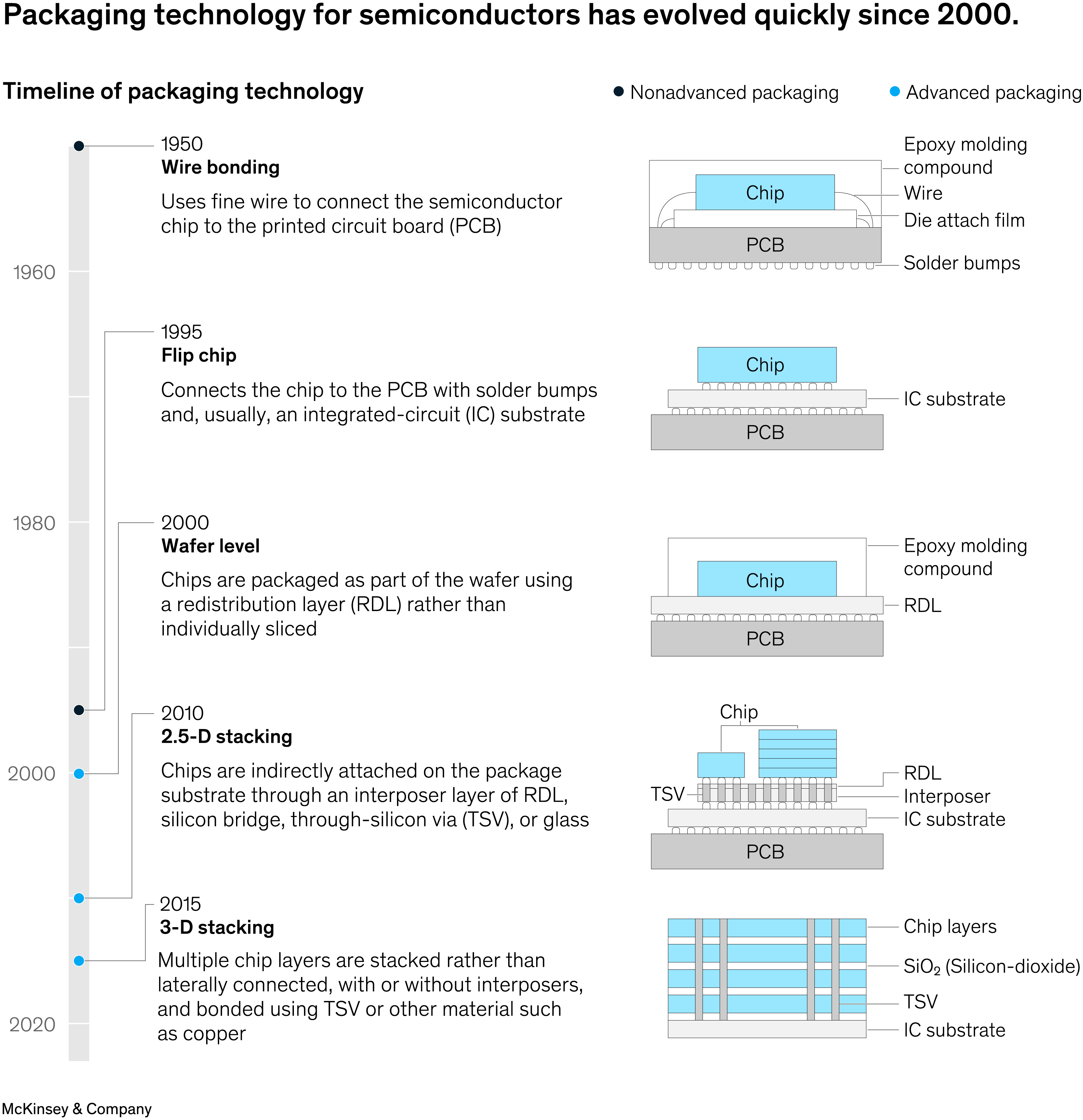

线键技术是一种互联技术,它利用焊球和细金属线将印刷电路板与芯片连接起来,这种技术在20世纪50年代开发,至今仍在使用。与封装芯片相比,它所需空间较小,可连接相对较远的点,但在高温、高湿和温度循环条件下可能会失效,而且每个键必须按顺序形成,这就增加了复杂性,并且减慢了制造速度。数据机构预测,到2031年,焊线亿美元,年复合增长率为2.9%。

封装技术的第一次重大演变出现在20世纪90年代中期的倒装芯片上,这种芯片使用面朝下的芯片,芯片的整个表面积都通过焊接凸点用于互连,将印刷电路板与芯片粘合在一起。这使得外观尺寸或硬件尺寸更小,信号传输速率更高,即信号从发射器到接收器的传输速度更快。倒装芯片封装是目前最常见、成本最低的技术,大多数都用在中央处理器、智能手机和射频系统级封装解决方案。倒装芯片能轻松实现更小的组装,并能承受更高的温度,但一定得安装在非常平整的表面上,而且不易更换。目前的倒装芯片市场规模约为270亿美元,预计年复合增长率为6.3%,到2030年将达到450亿美元。

先进封装技术,顾名思义,是对传统封装技术的升级与改进。传统的封装技术如线键合和倒装芯片虽然在过去半个世纪中发挥了巨大作用,但随技术的慢慢的提升和应用的多样化,其局限性也日益凸显。线键合技术虽然连接灵活,但在恶劣环境下容易失效,且制造速度较慢;而倒装芯片技术虽然实现了更小的组装尺寸和更高的信号传输速率,但对安装表面的平整度要求比较高,且不易更换。因此,寻找一种更高效、可靠的封装技术成为了行业的迫切需求。

自2000年以来,已有三种主要的先进包装技术投入商用,补充了上半个世纪盛行的两种技术。

先进封装有助于满足目前主流的新兴应用,例如5G、无人驾驶汽车和其他物联网技术,以及虚拟现实和增强现实技术。这些应用需要能快速处理海量数据的高性能、低功耗芯片。先进封装技术通过将多个芯片组合在一起,能轻松实现更高效的信号传输和数据处理,从而提升总系统的性能。

其次,先进封装技术可以通过优化封装结构和工艺,能够大大减少原材料的消耗和浪费,降造成本。同时,由于封装尺寸的缩小,也能够大大减少印刷电路板等配套设备的使用,逐步降低成本。并且,通过采用更先进的材料和工艺,可以有很大效果预防化学污染以及光、热和撞击的损害,来提升产品的常规使用的寿命和稳定性。

正是基于这些优势,先进封装技术自2000年左右推出以来,便获得了巨大的发展势头。目前,市场上已然浮现了多种先进的封装技术,如2.5-D、3-D、扇出式和系统级芯片(SoC)封装等。这些技术不仅弥补了传统封装技术的不足,还为半导体行业的发展带来了新的机遇。

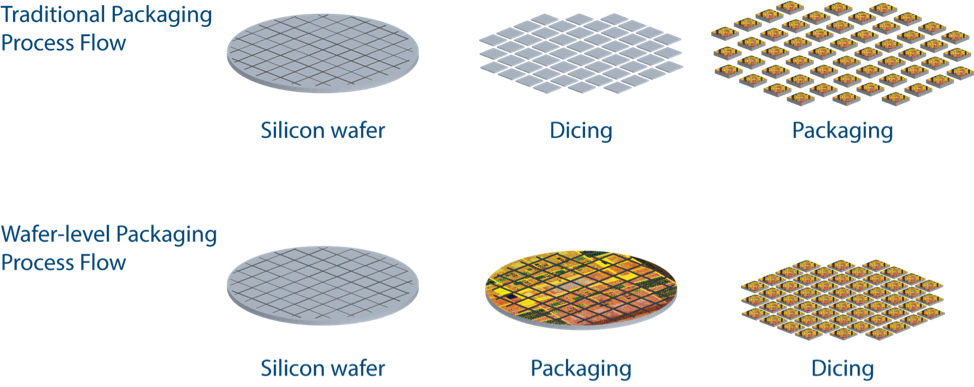

传统封装是先将硅晶圆切割成单个芯片,然后将芯片连接到印刷电路板并建立电气连接,而晶圆级封装则是在晶圆级进行电气连接和成型,然后使用激光切割芯片。就芯片配置而言,晶圆级芯片尺寸封装(WLCSP)与倒装芯片的最大不同之处在于,WLCSP的芯片与印刷电路板之间没有基板。相反,再分布层(RDL)取代了基板,从而缩小了封装尺寸并增强了热传导。

晶圆级封装分为两种类型:扇入式和扇出式。扇入式晶圆级封装大多数都用在技术方面的要求较低的低端手机,RDL走向晶粒中心。在2007年推出的扇出型封装中,RDL和焊球的尺寸超过了芯片的尺寸,因此芯片可以有更多的输入和输出,同时保持较薄的外形3。核心封装大多数都用在不需要高端技术的汽车和网络应用,如射频和信息娱乐芯片,在近15亿美元的扇出封装市场中占比不到20%。高密度和超高密度大多数都用在移动应用,预计将扩展到一些网络和高性能计算应用。全球最大的WLCSP制造商是台积电。

在过去的十年中,堆叠式WLCSP得到了充分发展,它允许在同一封装内集成多个集成电路,既可用于异质键合(集成逻辑芯片和存储芯片),也可用于存储芯片堆叠。在2.5-D堆叠中,两个或更多芯片并排放置,一个芯片与另一个芯片之间用中间件连接。2.5-D堆叠根据所使用的内插件种类可分为几类:

硅内插器是唯一需要TSV(即硅通孔)的类型,TSV是一种穿过硅芯片或晶圆的垂直电气连接。硅内插器使用的是一种稳定的技术,已在市场上使用了十多年,但硅的成本很高,而且需要前端技术和制造能力。台积电的CoWoS-S(晶片上基板芯片)在市场上占据主导地位。

硅桥相对较新。由于硅桥使用的硅量比传统硅内插器少,因此更薄,以此来降低了功耗,提高了设计灵活性。与传统硅插针相比,硅桥的优点是能轻松实现更先进的系统级集成,因此被用于人工智能等高性能计算(HPC)领域。有代表性的技术包括英特尔的EMIB(嵌入式多芯片互连桥)和台积电的CoWoS-L。

再分布层也可当作内插层。这种技术的最大优点是,创建RDL的光刻工艺可实现精细图案化,来提升速度和散热性能。台积电的CoWoS-R(基板上芯片RDL)即将开始批量生产。

玻璃也正在成为下一代内插材料。它在高频带宽下具有低成本和低功率损耗的特点,但可能在一段时间内还无法推向市场。

在三维堆叠中,多个芯片面朝下相互叠放,能够正常的使用或不使用中间膜。3-D堆叠主要有两种类型。最常见的是带微凸块(µ-凸块)的TSV。新的替代方法是无缓冲混合键合,使用介质键合和嵌入式金属形成互连;存储器厂商正在探索这种方法。

自2010年代中期以来,扇出式晶圆级封装一直占据主导地位,市场占有率约为60%。扇出封装比堆叠封装成本更低,而且具有高耐热性和小外观尺寸的特点。这些特性使其适用于移动应用,而移动应用可能会产生对扇出式封装的大部分需求。

苹果公司的应用处理器、图形芯片以及5G和6G调制解调器芯片采用扇出先进封装。苹果是该技术的最大用户,消耗了台积电生产的大部分产品。其他顶级无晶圆厂企业,即设计和销售硬件和芯片但外包生产的公司,也在大规模生产的芯片中使用扇出技术。

高性能计算和网络应用的大部分增长可能来自人工智能芯片、边缘计算和消费类设备中的网络芯片,它们需要扇出封装所能提供的小外观尺寸和经济实惠的成本。

最有可能推动2.5-D堆叠技术增长的可能是HPC应用,数据中心对这种应用的需求量很大。虽然2022年使用2.5-D堆叠技术的数据中心容量不到20%,但在未来五年内,这一比例可能会增加到50%。对于移动应用而言,2.5-D封装被认为成本过高,但随着下一代产品的到来,这样的一种情况可能会有所改变,因为下一代产品将采用成本更低的硅桥、RDL和玻璃中间膜。

在三维封装方面,存储器--三维堆叠的主要应用--以及SoC的使用预计将以大约30%的复合年增长率增长。慢慢的变多的高性能产品(包括高带宽内存(HBM)和带HBM的内存处理(PIM-HBM))将三维堆叠内存与逻辑芯片集成在一起,以此来实现了高带宽要求。对三维堆叠内存的大量需求可能来自数据中心服务器(需要大容量和高速度)、图形加速器和网络设备(需要尽可能大的内存和处理带宽)。

高性能计算系统,特别是中央处理器,将推动对3-DSoC芯片的需求。主要厂商在2022年开始采用混合键合技术,快速跟进者可能很快就会加入市场。由于技术门槛较高,OSAT、低级代工厂和集成设备制造商(IDM)不太可能进入市场。

先进封装技术的发展必然面临着一些挑战。首先,技术门槛较高,需要投入大量的研发资金和人力资源。其次,市场接受度尚需提升,由于新技术的推广和应用需要一段时间,因此初期可能面临市场需求不足的问题。此外,随技术的慢慢的提升,怎么样保持技术的领先性和创新性也是一个要关注的问题。

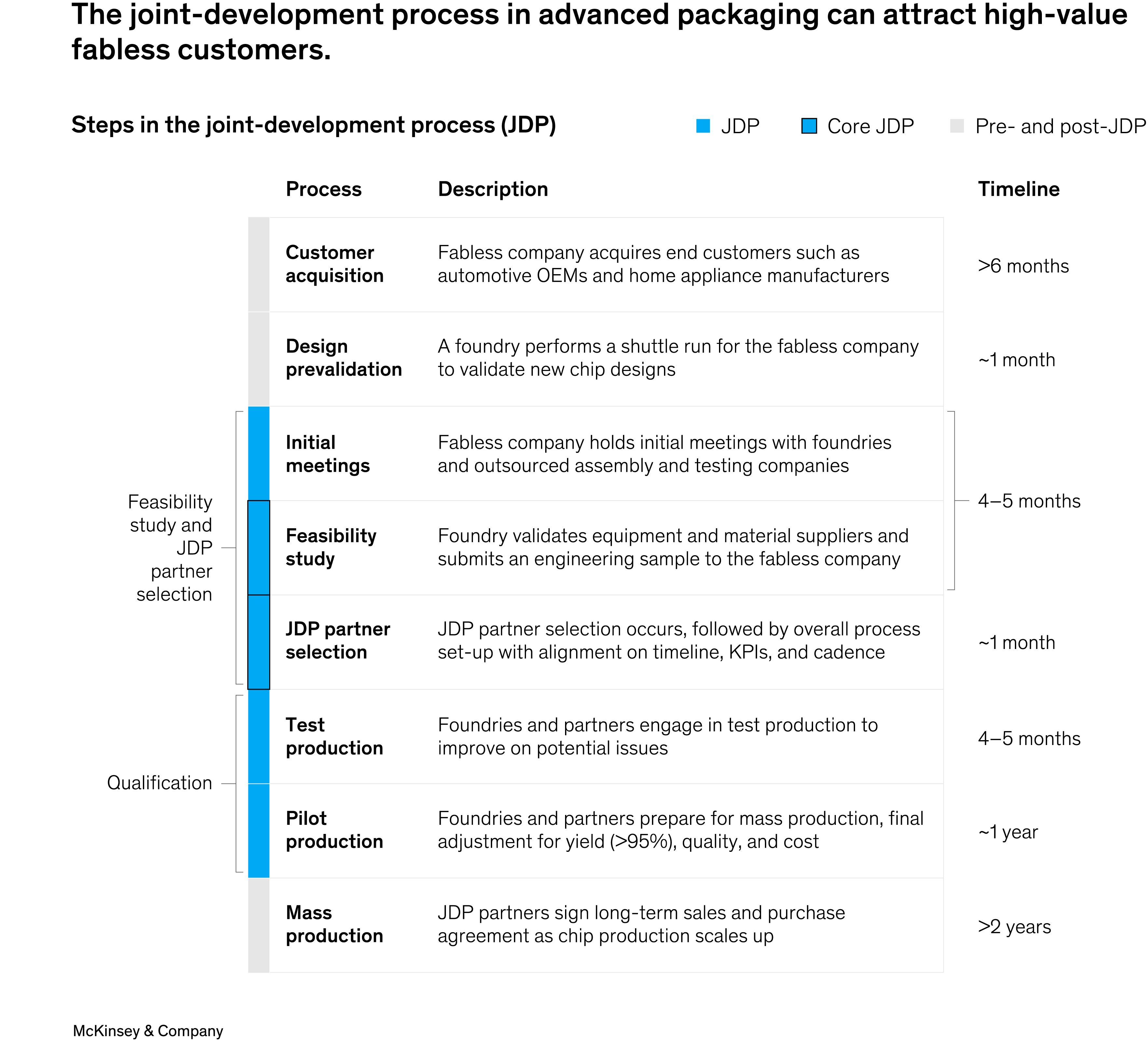

因此,为了获得并留住高价值的fab客户,制造商一定要能自如地开发高级封装解决方案。虽然fab厂商在开始大规模生产前完全掌控芯片规划流程,但制造商仍有增值空间。联合开发通常发生在芯片架构设计阶段和用于设计验证的初始穿梭运行阶段。由于对更高性能芯片的需求和封装造成的芯片设计复杂性的增加,预计这种合作的需求将会增加。

对于芯片制造商来说,另一个潜在的重要价值主张是确保设计能力和提供一站式解决方案--从设计到晶圆制造、封装和测试。

在制造方面,制造商要掌握2.5-D和3-D封装的两项关键技术能力,分别是中间膜和混合键合。就2.5-D而言,制造商一定要能利用新型材料和制造方法(包括硅、RDL和玻璃)处理新兴的内插器解决方案。对于三维技术,最新的混合键合技术方面的要求采用化学机械平坦化技术,以相同的平坦度抛光各种物质,防止出现凹陷,并通过设备和技术诀窍方面的磁盘到晶片能力实现高互连精度。

因此,尽管先进封装技术的市场足够引人注目,却也并非普通玩家可以进场的,唯有掌握核心技术的先驱者才能站稳脚跟。

上一篇:掌握3nm制程命脉应用材料展示七合一芯片工艺电阻降低50% 下一篇:半导体大会上吴汉明院士再度发声详解了国内半导体现状